Features

- Main PMC for USM Universal Submodules

- Conduction-cooled (CCPMC)

- 1 USM slot

- 1 FPGA 33,216 LE (for user-defined I/O and Nios soft core)

- 32 MB DDR2 SDRAM

- 2 MB Flash

- -40 to +85°C with qualified components

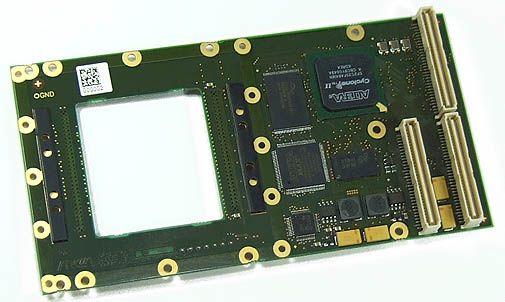

USM Universal Submodules make PMC modules more flexible than ever. The conduction-cooled main PMC P598 gets its specific function through the IP cores implemented inside the onboard FPGA. This function can be changed at any time through implementation of different IP cores. The corresponding line drivers are realized on the USM which is simply plugged on the P598.

The same USM may also be used on convection-cooled PMCs and XMCs or main M-Modules. A new design is then limited to the USM module and the FPGA content and therefore saves development time and costs. A Nios soft processor implemented in the Cyclone II FPGA by Altera provides local intelligence where needed.

The growing range of Wishbone-based standard IP cores from duagon comprise different UARTs, Ethernet, fieldbus interfaces, digital I/O etc. For users that like to write and/or implement specific IP cores on their own a complete development kit is available. The kit is based on a function-identical convection-cooled PMC module with front I/O.

The USM concept has been developed for harsh environment. Therefore, the P598 uses robust connectors to the USM, while all other components are soldered, and operates in a -40 to +85 °C temperature range with qualified components.

The P598 is a conduction-cooled PMC mezzanine card suitable for any compliant host carrier board in any type of bus system, i.e. CPCI, VME or on any type of stand-alone SBC. Appropriate carrier cards in 3U, 6U andother formats are available from duagon or other manufacturers.

Login